Advanced chiset features – BECKHOFF CX1020 Benutzerhandbuch

Seite 88

Montage und Verdrahtung

86

Embedded-PC

Advanced Chiset Features

In diesem Menu können Einstellungen zu den Funktionen des Speichers gemacht werden. Dabei sollte vorsichtig

vorgegangen werden, da Einstellungen hier die Stabilität des Gesamtsystems beinträchtigen können.

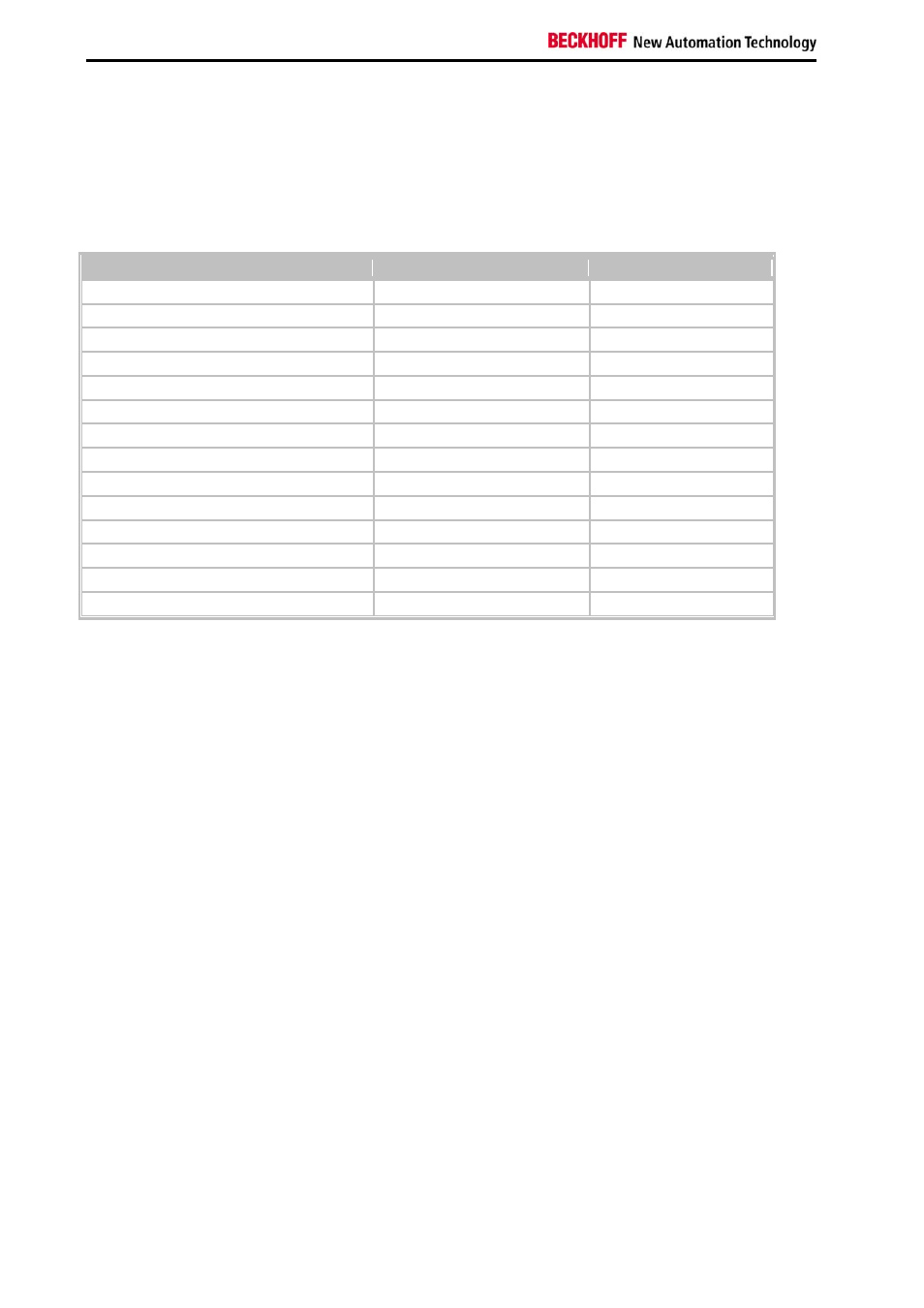

Phoenix – AwardBIOS CMOS Setup Utility

Advanced Chipset Features

DRAM Timing Selectable

[by SPD]

Item Help

CAS Latency Time

2.5

Active to Precharge Delay

7

DRAM RAS# to CAS# Delay

3

DRAM RAS# to Precharge

3

DRAM Data Integrity Mode

Non-ECC

MGM Core Frequency

[Auto Max 266 MHz]

System BIOS Cachable

[Enabled]

Video BIOS Cachable

[Disabled]

Memory Hole At 15M-16M

[Disabled]

Delayed Transaction

[Enabled]

AGP Aperture Size (MB)

[64]

** On-Chip VGA Setting **

On-Chip VGA

[Enable]

On-Chip Frame Buffer Size

[32MB]

↑ ↓ → ← :Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:Help

F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

DRAM Timing Selectable

Unter diesem Untermenü können Sie das optimale Timing für Optionen ein, je nach den von ihnen benutzten

Speichermodulen. Konfiguriert werden die Optionen über die Voreinstellung 'By SPD', indem der Inhalt des SPD

(Serial Presence Detect )-Gerätes ausgelesen wird. dabei werden im EEPROM kritische Parameter-Infos zu

Speichertyp, Größe, Geschwindigkeit, Spannungsinterface und Modulbänke abgespeichert.

CAS Latency Time

Unter dieser Option wird die Latenz zwischen dem DRAM -Lesebefehl und der zeit, zu welcher die Daten tatsächlich

zur Verfügung stehen, eingestellt. Einstellmöglichkeiten: 1.5 und 2.5

Active to Precharge Delay

Spezifizieren Sie die Zeitdauer, in der eine Speicherzeile (Row) offen gehalten wird, bevor ein Precharge erfolgt.

Standardmäßig wird dies durch den SPD zugewiesen. Einstellmöglichkeiten: 5, 6, 7, 8

DRAM RAS# to CAS# Delay

Diese Option regelt die Latenz zwischen dem aktiven DRAM-Befehl und dem Lese/Schreibbefehl.

Einstellmöglichkeiten 2 und 3

DRAM RAS# to Precharge

Der Wert gibt an, wie viel Zeit zwischen zwei Speicherzugriffen vergeht. Es reichen in jedem Fall vier Takte, drei

Takte sind zwar schneller, reichen aber nicht bei allen SIMMs aus. Man sollte die Einstellung auf Default lassen,

damit keine Speicherfehler entstehen.

DRAM Data Integrity Mode

Diese Option hängt stark mit der Option ECC Test (Error Checking and Correction) zusammen. Sie legen hier eine

wenig optimale Paritätsprüfung fest, die Fehler nur erkennt, aber nicht beseitigt. Einstellungen: Non-ECC (dürfte für

die meisten von Ihnen richtig sein) und ECC. Wenn Ihr Speicher ein ECC-Speicher ist, dann wählen Sie die Option

ECC.

MGM Core Frequency

Diese Funktion stellt die Geschwindigkeiten für den FSB ein. Dabei werden die Parameter zu Graphicspeicher und

Prozessorkern ebenfalls gesetzt. Es empfiehlt sich die Einstellungen auf Auto Max 266 zu belassen.